Intel 最新 10nm 技術改名為「Intel 7」,新製程路線圖看向「埃」時代

Intel 今日稍早詳細公開了最新的製程與封裝技術規畫,不僅帶來了極具野心的新時程,同時也重新命名了其節點,將其節點與物理尺寸脫勾。目前對於節點的命名(也就是我們常說的「幾奈米」)是以半導體上最小的零組件尺寸為基礎,雖然說就廣義上來說代表示技術演進的世代,但就算是這些零組件本身,也會因為結構和技術,而在性能上有著差異。這使得 Intel 的 10nm 技術有著雖然與他廠 7nm 類似的性能表現,但在紙面上看起來就是差了一個世代。

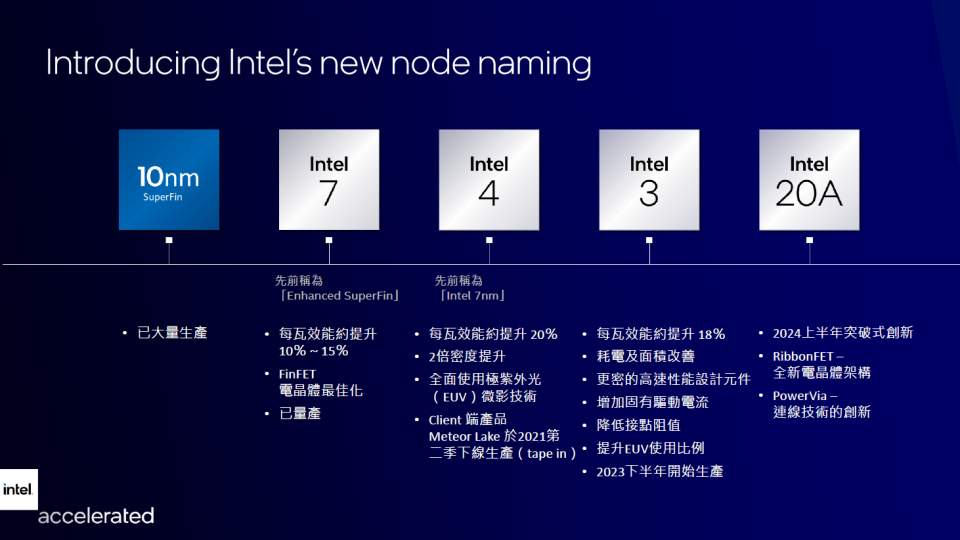

因此 Intel 將在節點命名中捨棄直接使用奈米數,而是將節點「概念化」,將即將上市的 10nm Enhanced Superfin 改名為「Intel 7」,並且隨後推出「Intel 4」、「Intel 3」等,依此類推。Intel 7 依然是以 FinFET 技術的最佳化為主,相較於目前最新的 10nm SuperFIN,每瓦效能約可提升 10~15%。Intel 7 將會用在今年底的 Alder Lake 筆電處理器與明年初的 Sapphire Rapids 資料中心處理器上。Intel 4 則是使用極紫外光(EUV)微影技術來進行微縮,預計每瓦效能可以再提升 20%,並將在 2022 年下半年開始量產,2023 年開始出貨。率先採用 Intel 4 的產品預計為再次世代的 Meteor Lake 消費型處理器與 Granite Rapids 資料中心處理器。而 Intel 3 則是 FinFET 的最後一次登場,運用 FinFET 與 EUV 的再進一步最佳化,實現相較於 Intel 4 再 18% 的每瓦效能成長。Intel 3 預計 2023 下半年開始生產。

由 Intel 3 再往後,Intel 便將進入「埃」時代。埃(Angstrom)是 0.1nm 的長度,因此下一個節點的「Intel 20A」其實等同於 2nm 的意思。Intel 20A 將引入兩個突破性的新技術「RibbonFET」與「PowerVia」,前者為 Intel 新的環繞式閘極的實作成果,能在較小的面積中垂直疊放多個鰭片,在縮小面積的同時,也能用相同的電流提供更快的電晶體開關速度。PowerVia 則是將晶片正面供電的迴路與訊號傳遞的回路分離,移到晶片的背部。如此一來就能避免供電與訊號之間的干擾,最佳化訊號的傳遞。Intel 20A 預計 2024 年量產,而 Intel 已經找上了 Qualcomm 做為未來採用 Intel 20A 製程技術的客戶。最後,由 Intel 20A 改良的 Intel 18A 也已進入開發階段,預計 2025 年初問世,Intel 並且已經與 ASML 在合作當中,開發名為「高數值孔徑 EUV」的未來生產工具。

仔細算一下的話,由現在到 2025 年初之間,Intel 將要追 5 個節點,並且在中間進行至少一次的技術轉換,野心不能說不大。但自然在這期間競爭對手也不會在原地踏步,Intel 就算能以高速追趕,恐怕要回到過去主宰市場的位置也不是一蹴可幾的了。不過對於我們消費者來說,有高度的競爭才是好事,也希望 Intel 能真的照著路線圖走,持續保持著競爭力囉。

雅虎香港新聞

雅虎香港新聞